AMD throws Epyc launch in Austin to celebrate its return to the data center.

It was a triumphant Lisa Su and Forrest Norrod who took the stage at Austin’s Long Center to declare AMD has returned to challenge Intel in the server market with Epyc, their new server product based on the Zen architecture. In fact, the stage was packed with AMD executives and partners who all praised the return of AMD.

Lisa Su told the audience, “the single biggest bet for our company is success in the data center,” citing a $21 billion total available market.

https://youtu.be/GkFEseXY4A0

The company announced product partnerships with HPE, Dell, Lenovo, Samsung Electronics and SuperMicro, and also deals with Mellanox, VMware, and Xilinx.

Presenting a strong story for their presence in the ecosystem

AMD has been extraordinarily systematic in the lead-up to its Epyc introduction. The company has been preparing the market step by step with the introduction of its Zen CPU technology, its Ryzen product for commercial markets, and now Epyc for the enterprise.

At the Epyc launch in Austin, Lisa Su said AMD is here to stay as she showed a roadmap of products. This is a statement Su has been making at every presentation since the announcement of Zen’s arrival in March 2017.

Epyc—a chip with a system in it

The Epyc family of processors features more cores, more I/O, more intelligent power management, more security, and more memory than anything else in the market today.

The headline features are:

- Up to 32 High-Performance “Zen” Cores

- 8 DDR4 Channels per CPU

- Up to 2TB Memory per CPU

- 128 PCIe Lanes

- Dedicated Security Subsystem

- Integrated Chipset

- Socket-Compatible with Next Gen EPYC Processors

Built in 14 nm at Global Foundries’ fab, the chip is as close as you can come to integrating an entire computer in one chip—a CoC.

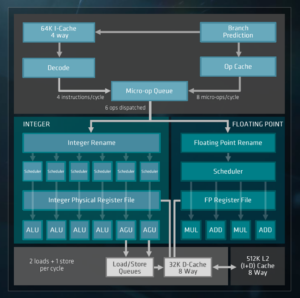

Get your Zen on

As mentioned, AMD has designed the Zen core for the data center; they’ve made that clear from the first open discussions at Hot Chips last year. It will drive up to 64GB of physical memory and hold a translation resident from the L1 TLB with 1G pages. That is used to reduce the time taken to access a user memory location. It is a part of the chip’s memory-management unit (MMU).

It can perform up to 3G of physical memory translation resident in the TLB5 with 2M pages. And it can do a coalescence of 4K pages into 32k pages which allows for residency of 48M of memory. That’s all stuff that makes users of big data smile.

AMD has also built-in virtualization enhancements, targeted at the data center, which include:

- Virtualized APIC to handle guest level APIC accesses without a world switch

- Dual Translation Table engines to load the TLBs

- 64 Entry upper level translation table page walk cache

- Coalesced page directory level nested translation table entries stored in the L2 DTLB Reduces TLB translation from worst case 24 data accesses to 1 data access

And it has cryptographic enhancements that include dual AES units to accelerate single threaded algorithms or increase throughput with simultaneous multithreading (SMT), as well as secure hash algorithm (SHA) instruction support to hardware accelerated SHA-1 and SHA-256 algorithms, with keys for accelerating workloads.

AMD’s Epyc is an MCM (multi-chip module) that combines four ZEN-based CPUs, which AMD refers to as the MCM complex. A CPU complex (CCX) is four cores connected to an L3 Cache. The L3 Cache is 16-way associative, 8MB, mostly exclusive of L2. The L3 cache is made of 4 slices, by low-order address interleave. Every core can access every cache with same average latency, and the chip utilizes the upper level metals for high frequency data transfer. AMD says multiple CCXs can be instantiated at SOC level.

One socket or two?

AMD is bringing the argument that their single socket Epyc is competitive with a dual socket solution from competitors, offering better price-performance metrics. And in comparison to Intel, the Epyc single socket product will have the full 128 PCIe to use for adding GPUs and storage.

The 2P design also uses AMD’s Infinity Fabric Interconnect, and has Integrated SCH which removes platform components, and offers 64c/system for I/O and compute balance.

Communications and power

Two of the most interesting aspects of the device are the fabric and the power management. The fabric builds on AMD’s innovative hyper-transport technology that they brought to the PC in 2001, and in addition to connecting the four CPUs within Epyc, extends outward to external CPU, making it possible to build cube structures.

AMD has come up with an intelligent and high-speed power regulator. AMD says there are thousands of sensors in the chip that monitor voltage, temperature, and clock. They are monitored by a dedicated processor which can make fine grained adjustments within a millisecond to give the maximum power to any core that has a job and turn down cores that are idle. This capability allows the company to provide a guaranteed level of performance (important to server farms that need deterministic performance for QoS, and other obligations), while offering the opportunity to reduced power consumption. This intelligence extends to the hyper-links a well, adapting the bandwidth to the workload needs. As a result AMD claims they can realize between a 1.54 to 1.76 performance/watt gain with 41% to 55% less energy consumption.

AMD says the Epyc has been built for the future. It has over-provisioned the I/O, there are new chips in the pipeline, and the GlobalFoundries fab is performing well.

AMD SVP and CTO Mark Papermaster told a group of press and analysts at a preliminary event, “we didn’t just wake up and back into this. At AMD we had a decision to make almost 5 years ago when we had major investment decisions to make.” Their decisions around the architecture of the Epyc at that time were a response to the explosion of data already gathering speed. Papermaster says, “we saw clearly the start of a whole new sector” which will take advantage of machine learning and AI for big data.

In addition, the company says, they see their use of MCM as a harbinger of the future as Moore’s Law hits its inevitable ceiling.